## **EARDA**

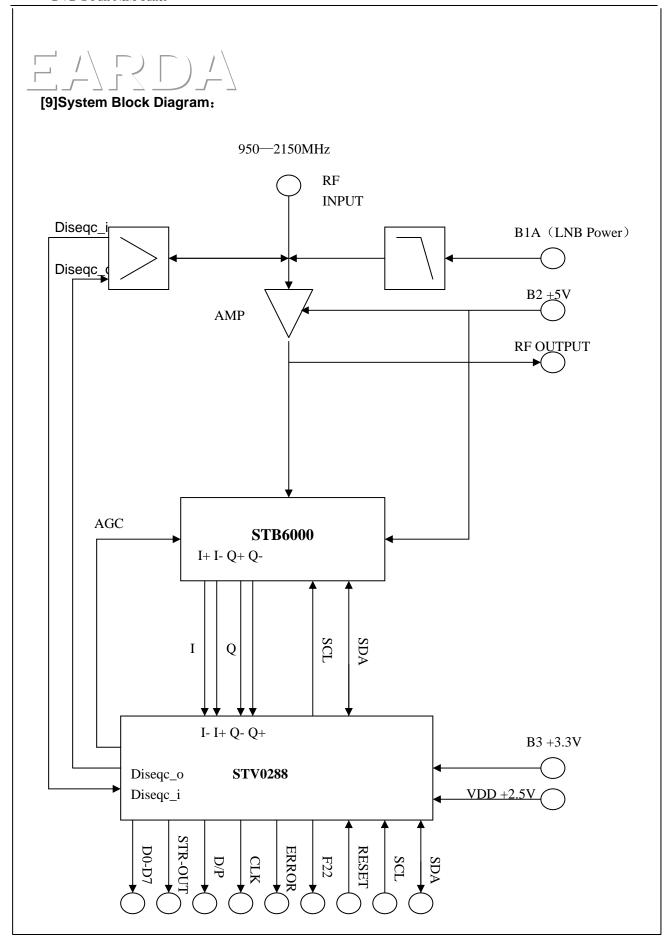

EDS-1547FF1E+ DVB-S Full NIM Tuner

### **SPECIFICATION**

| Taigo RF Technology (HK) Ltd Earda Technology Ltd. |                                           |  |                      |  |

|----------------------------------------------------|-------------------------------------------|--|----------------------|--|

| DSGD.                                              | CHKD. APPD. PRODUCT: DVB-S Full NIM Tuner |  |                      |  |

|                                                    |                                           |  | MODEL: EDS-1547FF1E+ |  |

|                                                    |                                           |  | DATE: 2008.09.10     |  |

### Z/\RD/\

#### [1]GENERAL SPECIFICATIONS

■ Input frequency

■ Output frequency

■ Input signal level

950MHz — 2150MHz

950MHz — 2150MHz

-65dBm — -25dBm

■ Input connector■ Output connectorF-Connector

■ Input impedance  $75 \Omega$ ■ Output impedance  $75 \Omega$

■ Channel selection system

■ LINK IC

PLL synthesizer (Clock 4.0MHz. Address: C6(HEX))

STV0288 (CLOCK: 4MHz, Address: D0 (HEX))

■ Operating voltage LNB power supply 25V DC, 400mA(MAX.)

B2:  $+5V \pm 0.25V$ B3:  $+3.3V \pm 0.165V$ VDD:  $+2.5V \pm 0.125V$

■ Temperature  $0^{\circ}$  ~ +60° C

Storage:-20°C ~ +70°C

■ Humidity Operating: Less than 85%

Storage: Less than 95%

#### **KEY FEATURES**

■ DVB-S / DIRECTV<sup>TM</sup> full NIM tuner with autoscan feature

■ Symbol rate 1 ~ 45Msps

■ Fast channel acquisition

- High speed scanning mode for blind symbol rate acquisition

- Full satellite transponders scanning in seconds

- Up to 60 Msps operation

- DiSEqC<sup>TM</sup>2.x

- Receive and transmit for full control of LNB And switchers

#### **MULTISTANDARD DECODING**

- DIRECTV<sup>TM</sup> system /DVB-S

- VITERBI soft decoder rate 1/2

- Puncture rates are 1/2,2/3,3/4,5/6,6/7,7/8

- Outer Reed-Solomon decoder as per DVB-S and DIRECTV<sup>TM</sup> system

- Energy dispersal descrambler

#### **INTERFACES**

- Data to transport decoder

- DVB common interface compliant

- 12-bit parallel and 5-bit serial data interface with Data on D0...D7 (packer error private

#### line)

- Transport bit rate automatic regulation with regard to transport clock

- I<sup>2</sup>C serial bus interface

- Fast I<sup>2</sup>C up to 4 MbPs slave interface

- 4 possible slave addresses

- Up to 400 KbPs private repeater for tuner isolation

- DiSEqC<sup>TM</sup> 2.x

- 22KHz to 100 KHz interface

- GPIOs and interruption line

- lock indicators: AGC carrier, timing, VITERBI-decoder

- Monitoring through I<sup>2</sup>C serial interface

- C/N estimator-signal strength indicator

- IQ constellation display

- BER and PER estimator

- Bit and packet error count

### [2]ELECTRICAL SPECIFICATION

| Item Condition            |                                                                                                   |         | Specification |      |      |      |

|---------------------------|---------------------------------------------------------------------------------------------------|---------|---------------|------|------|------|

| item                      | Condition                                                                                         |         | Min.          | Тур. | Max. | Unit |

| RF input VSWR             | 950MHz —— 2150MHz                                                                                 |         |               | 2.0  | 2.5  |      |

| RF output VSWR            | 950MHz 2150MH                                                                                     | lz      |               | 2.0  | 2.5  |      |

| RF output gain            | 950MHz — 2150MH                                                                                   | lz      | -2            | 0    | +2   | dB   |

| Noise figure              | 950MHz —— 2150                                                                                    | MHz Max |               | 8    | 12   | dB   |

|                           | gain                                                                                              |         |               |      |      |      |

| Intermodulation rejection | Input level -25dBm                                                                                |         |               |      |      |      |

| Desired signal Fo         | I/Q Output level 0.6Vp_p                                                                          | )       |               |      |      |      |

| Undesired signal(2        | 1KΩ load                                                                                          |         | 40            | 60   |      | dB   |

| signals)                  |                                                                                                   |         | 40            | 00   |      | uБ   |

| (Fo+29.5MHz,Fo+59MHz) or  |                                                                                                   |         |               |      |      |      |

| (Fo-29.5MHz,Fo-59MHz)     |                                                                                                   |         |               |      |      |      |

| Local oscillation signal  | 950MHz 2105MH                                                                                     | lz      |               | -72  | -68  | dBm  |

| Leak at input terminal    |                                                                                                   |         |               |      |      |      |

| Local oscillation signal  | 950MHz —— 2150MHz                                                                                 |         |               | -67  | -63  | dBm  |

| Leak at output terminal   |                                                                                                   |         |               |      |      |      |

| Eb/No                     |                                                                                                   | PC= 1/2 |               | 3.7  | 4.5  | dB   |

| (BER=2×10 <sup>-4</sup>   | $4 \le Fs \le 35 [Mbaud]$ (Fs: Symbol rate) $PC = 3/$ $PC = 5/$                                   | PC= 2/3 |               | 4.2  | 5.0  | dB   |

| at Viterbi output)        |                                                                                                   | PC= 3/4 |               | 4.7  | 5.5  | dB   |

|                           |                                                                                                   | PC= 5/6 |               | 5.3  | 6.0  | dB   |

|                           |                                                                                                   | PC= 7/8 |               | 5.7  | 6.4  | dB   |

| Eb/No (Low rate)          |                                                                                                   | PC= 1/2 |               | 4.8  | 5.5  | dB   |

| (BER=2×10 <sup>-4</sup>   | 1 < Ec. / [Mbaud]                                                                                 | PC= 2/3 |               | 5.0  | 6.0  | dB   |

| ,                         | 1 ≦ Fs<4[Mbaud]<br>(Fs: Symbol rate)                                                              | PC= 3/4 |               | 5.5  | 6.5  | dB   |

| at Viterbi output)        | (1 S. Symbol rate)                                                                                | PC= 5/6 |               | 6.2  | 7.0  | dB   |

|                           |                                                                                                   | PC= 7/8 |               | 6.8  | 7.4  | dB   |

| Eb/No(High rate)          |                                                                                                   | PC= 1/2 |               | 4.4  | 5.4  | dB   |

| (BER=2×10 <sup>-4</sup>   | 25.5c 5/1/160.1d1</td <td>PC= 2/3</td> <td></td> <td>5.1</td> <td>6.1</td> <td>dB</td>            | PC= 2/3 |               | 5.1  | 6.1  | dB   |

| •                         | 35 <fs 45[mbaud]<="" td="" ≦=""><td>PC= 3/4</td><td></td><td>6.0</td><td>7.0</td><td>dB</td></fs> | PC= 3/4 |               | 6.0  | 7.0  | dB   |

| at Viterbi output)        | (Fs: Symbol rate)                                                                                 | PC= 5/6 |               | 6.9  | 7.9  | dB   |

|                           |                                                                                                   | PC= 7/8 |               | 7.5  | 8.5  | dB   |

|                           | B2=5V                                                                                             |         |               | 200  | 220  | mA   |

| Current consumption       | B3=3.3V                                                                                           |         | 10            | 50   | mA   |      |

|                           | VDD=2.5V                                                                                          |         | 250           | 350  | mA   |      |

#### [3]PLL FUNCTIONAL DESCRIPTION

I<sup>2</sup> C BUS DATA FORMATS

Table1: Write data format (MSB is transmitted first)

| Sub address | B7   | B6   | B5   | B4   | В3   | B2   | B1   | B0   |

|-------------|------|------|------|------|------|------|------|------|

| 01          | OSCH | OCK1 | OCK0 | ODIV | OSM3 | OSM2 | OSM1 | OSM0 |

| 02          | N8   | N7   | N6   | N5   | N4   | N3   | N2   | N1   |

| 03          | N0   | 0    | 0    | A4   | А3   | A2   | A1   | A0   |

| 04          | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    |

| 05          | 0    | 0    | 0    | 0    | G3   | G2   | G1   | G0   |

| 06          | 0    | 0    | 0    | F4   | F3   | F2   | F1   | F0   |

| 07          | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0    |

| 08          | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0    |

| 09          | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    |

| 0A          | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 1    |

| 0B          | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1    |

#### OSCH, OCK1-0, ODIV, OSM3-0 (Reg01):

| LO. Frequency | Data (HEX) | LO. Frequency (MHz) Data HEX) |

|---------------|------------|-------------------------------|

| (MHz)         |            |                               |

| 950999        | BA         | 1470——1529 A5                 |

| 10001075      | BC         | 1530——1649 A6                 |

| 10761199      | A0         | 1650——1799 A8                 |

| 1200——1299    | A1         | 1800——1949 AA                 |

| 13001369      | A2         | 1950—2150 AC                  |

| 13701469      | A4         |                               |

N8—N0: Programmable division ratio N control bits, Npro:0—511.

$N_{pro} = N8 \times 2^8 + N7 \times 2^7 + \dots + N2 \times 2^2 + N1 \times 2^1 + N0 \times 2^0$ .

A4—A0: Programmable division ratio A control bits, Apro:0—31.

$A_{pro} = A4 \times 2^4 + A3 \times 2^3 + A2 \times 2^2 + A1 \times 2^1 + A0 \times 2^0$ .

NOTE: N and A Calculate:

A. LO. Frequency: 950MHz to 1075MHz:

$N_{pro}=f_{RF} (MHz) \div 8,$

Apro=fRF (MHz)  $\times$ 2-Npro $\times$ 16;

B. LO. Frequency: 1076MHz to 2150MHz:

$N_{pro}=f_{RF}$  (MHz)  $\div 16$ ,

$Apro=fRF (MHz) -Npro \times 16$

G3—G0: IQ Gain Setting:

1110: +14 dB 0111: 0dB 0010: -10dB

F4—F0: Base band filter setting bits:

$F_{pro} = F4 \times 2^4 + F3 \times 2^3 + F2 \times 2^2 + F1 \times 2^1 + F0 \times 2^0$ .

NOTE:

A: If symbol rate(Sb) less than 30MHz,  $F_{pro} = Sb(MHz)$ ;

B: If symbol rate(Sb) is 30MHz to 45MHz, Fpro =30.

#### [4] CONFIGURATION REGISTERS

STV0288 I2C Chip Address Selection

| Tuner Pin 7 Voltage | Write Address | Read Address |  |

|---------------------|---------------|--------------|--|

| 0(GND or Open)      | D0hex         | D1hex        |  |

| 1(+3.3V)            | D2hex         | D3hex        |  |

Please refer to STV0288 datasheet for the programming.

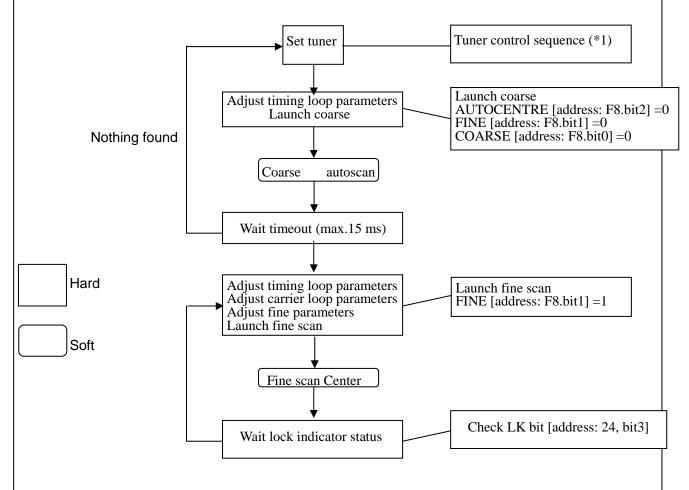

#### [5] Fast channel acquisition and blind search

Automatic symbol rate search, signal acquisition and signal tracking are built into the STx0288 using a simple state machine controlled by I<sup>2</sup>C commands. The state machine significantly reduces the software needed and also decreases the duration of the transponders acquisition.

#### 5-1 Control

The fast channel acquisition is performed in two steps. First step 'coarse auto search' enables rough estimation of a QPSK carrier within a given RF bandwidth. Second step 'Autos can' enables automatic lock to the previous estimated QPSK carrier.

#### 5-1-1 First step: coarse auto search

- Coarse carrier and symbol frequency search

- Find appropriate symbol and carrier frequency in about 15 ms after tuner programming

- Range 1 to 45 Msps

- Accuracy of the estimation:

-carrier offset: ~ 1% Fs -symbol rate: ~ 5%

#### 5-1-2 Second step: autoscan

- Automatic symbol frequency scanning in any range.

- Automatic stop when the chip is locked

- Needs 1 Msymb to scan even at low C/N (3.5 dB)

#### 5-2 Results

- Simplified scanning software routine versus STx0288

- Full satellite scanning in some seconds

- Fast channel acquisition

- -Typical 15ms + 1 Msymbol duration

- -Less than 120ms if fs > 10 MBd (channel unknown a priori)

- -Around 5s around 2Msps (channel unknown a priori)

#### 5-3. FLOW CHART

The following flow charts show recommended internal PLL and STB0288 control flows.

\*1 Tuning details is down in the next section.

#### [6] PLL Programming Sequence:

- 1. Open I<sup>2</sup> C bus repeat;

- 2 \ I<sup>2</sup> C bus start:

- 3、Write address:

- 4. Write sub address:

- 5. Write Reg01h to Reg0Bh data;

- $6 \cdot I^2 C$  bus stop;

- 7. Close I<sup>2</sup> C bus repeat;

- 8. Open I2 C bus repeat;

- 9 \ I<sup>2</sup> C bus start:

- 10 Write address:

- 11. Write sub address:

- 12. Write data;

- 13 Write data:

- 14. Write data;

- 15. Write data;

- 16.  $I^2$  C bus stop;

#### After tuner lock:

- 1. Open I<sup>2</sup> C bus repeat;

- 2 \ I<sup>2</sup> C bus start;

- 3、Write address (C6h);

- 4、 Write sub address;

- 5、Write data;

- $6 \cdot I^2 C$  bus stop;

#### NOTE:

Gain control: High input voltage corresponds to high gain

Please refer to the STB6000 and STV0288 datasheet for the programming

#### 7 DiSEqC 2.x interface

#### 7-1 Transmit DiSEqC interface

The transmit DiSEqC interface simplifies the real-time dialog between the microprocessor and the LNB. Using the I<sup>2</sup>C bus, the microprocessor fills an 8-byte FIFO, and then transmits the data by modulating the F22TX clock (F22TX is set to 22kHz beforehand).

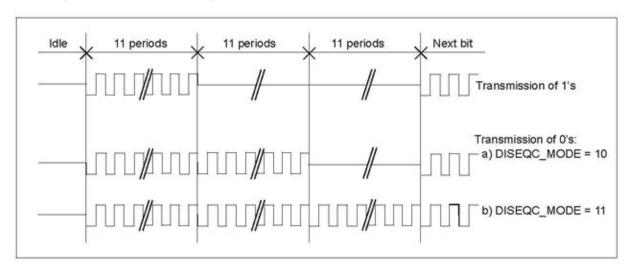

#### 7-1-1 Modulation.

Figure 2: Schematic showing bit transmission

The output is a gated 22 kHz square signal

- In idle state, modulation is permanently inactive.

- In byte transmission, the byte is sent (MSB first) and is followed by an odd parity bit.

A byte transmission is therefore a serial 9-bit transmission with an odd number of 1's.

Each bit lasts 33 F22 periods, and the transmission is PWM-modulated.

#### Transmission of 0's

There are two sub modes controlled by the I2C bus:

- modulation is active for 22 pulses, then inactive for 11 pulses (2/3PWM).

- modulation is active for 33 pulses (3/3 PWM). Transmission of 1's During transmission of 1's, modulation is active for 11 pulses, then inactive for 22 pulses (1/3 PWM).

This is compatible with tone burst in older LNB protocols.

For the modulated tone burst, only one byte (with value 0xFF) is written to the FIFO. The parity bit is 1. As a result, the output signal is nine 0.5 ms bursts, separated by eight 1-ms intervals. For the unmodulated tone burst, DISEQC\_MODE = 11 and only one byte of value 0x00 is sent. The parity bit is still 1. As a result, the signal is a continuous series of 12.5 ms.

When the modulation is active, the DiSEqC output is forced alternatively to VDD and VSS levels.

#### 7-1-2 Envelope mode

In envelope mode, a 22-kHz envelope output is generated instead of a modulated signal output. It controls the on/off switch of an external 22-kHz oscillator.

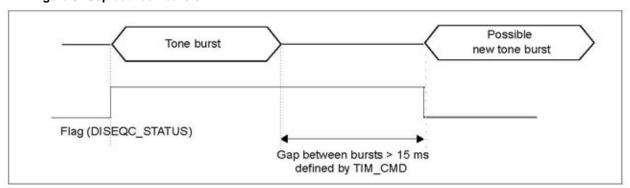

Figure 3: Gap between bursts

The backward compatibility of DiSEqC requires a 15-ms gap after a tone burst sequence. This information is delivered by a flag in a status register. This flag is set at the beginning of the transmission, and is reset after a time which includes both the transmission and a period defined by the I2C bus.

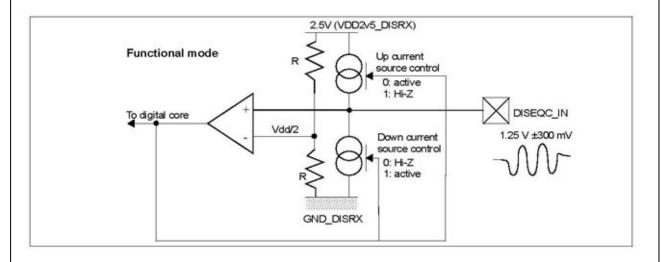

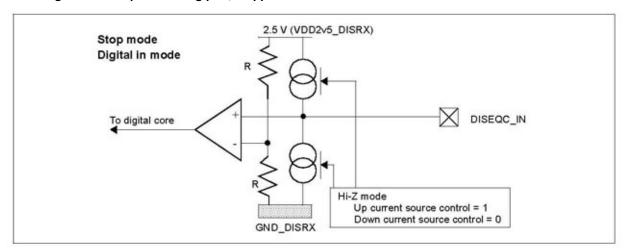

#### 7.2 DiSEqC receive interface

The DiSEqC receive interface is composed of three parts, one analog and two digital.

- Analog: bypassable 1-bit analog-to-digital conversion,

- Digital filtering: envelop detection,

- Digital treatment: received byte extraction and stacking in FIFO, status management.

Figure 4: DiSEqC Rx analog part, running mode

Figure 5: DiSEqC Rx analog part, stopped mode

General cell characteristics are as follows:

- 8-byte FIFO,

- bypass mode for analog cell: the signal can be provided by a pin other than DISEQC\_IN (or inverted DISEQC\_IN), IP0 or IP1 may be used, inverted or not,

- envelope mode: bypass of digital filtering,

- IRQ signals: fourth byte stacked in the FIFO and end of reception,

- 16-bit status register

- FIFO and parity output registers, a non-null value in DISPARITY indicates a transmission error in the remaining data still stacked in the FIFO,

- other features:

- ignore short 22-kHz mode: does not consider pulses composed of less than seven 22-kHz waves,

one-chip test mode: DISEqC Tx signal is injected in the DiSEqC Rx cell so the decoder understands the encoder.

- · continuous tone detection, decoding fail detection and alert,

- 22-kHz frequency generation register: F22RX. The fully digital construction and independence of the analog cell enables the standard 22kHz to be increased up to 100kHz.

#### [8] Reliability

- 8-1. High temperature high humidity load (40°C, 90% RH, 500h)

- 1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial value

- 2) After cycling DUT in the constant chamber at 40°C/90-95% RH for 1.5h in on state and for 0.5h in off state, for total 500h, leave the DUT at room temperature and humidity for 2h and then measure value after test.

- 3) Must meet the specifications of Table 9-1.

- 8-2. High temperature load (70°C, 40% RH, 500h)

- 1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial value.

- 2) After leaving DUT in the constant chamber at 70±2℃/40% RH for total 500h, leave the DUT at room temperature and humidity for 2h and then measure value after test.

- 3) Must meet the specifications of Table 9-1.

- 8-3. Cold test (-25°C, 500h)

- 1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial value.

- After leaving DUT in the constant temperature chamber at -25℃ for 500h,leave the DUT at room temperature and humidity for 2h and then measure the values after test.

- 3) DUT must meet the specifications given in Table 9-1.

- 8-4. Shock (686 m/s2, 6 planes, 3 times)

- 1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial values.

- Using the shock tester, apply shock of 686m/s2 three times to each of 6 planes and then measure the values.

- 3) DUT must meet the specifications given in Table 9-1.

- 4) This test is to be conducted using a single tuner.

- 8-5 Vibration (10-55 Hz, 1.5 mm, in each of three mutually perpendicular directions, each 2 times)

- 1) After leaving DUT at room temperature and humidity for 24h or longer, measure the initial values.

- 2) Using the vibration tester, apply motion having an amplitude of 1.5mm (constant), the frequency being varied uniformly between 10 and 55 Hz, to DUT, for 2 hours in each of three mutually perpendicular directions (X, Y and Z, total of 6 hours). After the test, measure the values.

- 3) DUT must meet the specifications given in Table 9-1.

- 4) This test is to be conducted using a single tuner.

- 8-6 Solderability of terminal Pretreatment of heating terminal at  $150^{\circ}$ C for 1h is performed and leave it at room temperature for 2h or longer. Immerse 1.9 mm length of terminal (from the tip) to be soldered into rosin (JIS-K-5902), isopropyl alcohol (JIS-K-8839 or JIS-K-1522, rosin concentration (10-35% range) approx. 25% by weight unless otherwise specified) or equivalent solution for 3–5s, and then immerse the length of the terminal into a pool of molten solder (Sn/3.0Ag/0.5Cu, or equivalent) at 240  $\pm 2^{\circ}$ C for 3s. Dipped terminal portion shall be wetted by more than 95%.

- 8-7 Soldering heat resistance immerse the terminal mounted on a PCB(1.6t thick) into solder at  $350\pm5$  °C for 3.0-3.5 seconds or at  $260\pm5$ °C for  $10\pm1$  seconds. Remove the PCB from the solder and leave it for 1 hour at room temperature. The test sample shall show no degradation in appearance and electrical characteristics.

### 8-8 ESD protection

#### ESD test condition(IEC61000 4-2 compliant)

| terminal              | limits        | Condition                 |  |

|-----------------------|---------------|---------------------------|--|

| RF_IN(coaxial center) | $\pm$ 15kV DC | 150pf/300ohm each 5 times |  |

| Others                | ±200V DC      | 150pf/300ohm each 5 times |  |

| Item  | Specification              | Condition                  |

|-------|----------------------------|----------------------------|

| Eb/No | (initial Values) $\pm$ 1db | BER=2e-4 at viterbi output |

|       |                            | PC=3/4                     |

| /\ |  | /    |

|----|--|------|

|    |  | _/ _ |

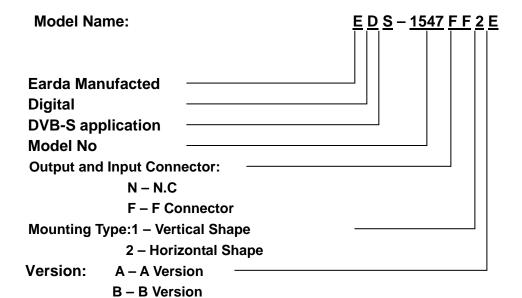

### [10] Ordering Information

C – C Version

D – D Version

E – E Version

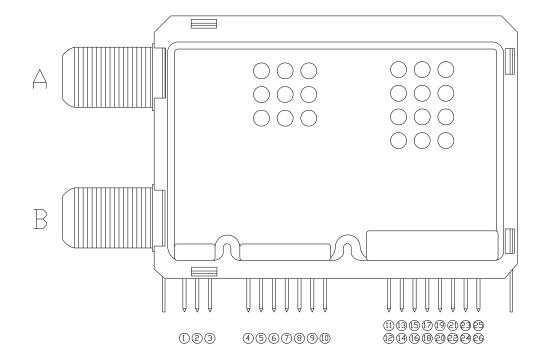

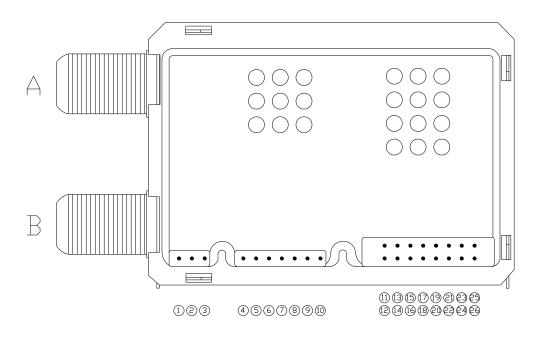

[11] Pin difinition EDS-1547FF1E+

#### EDS-1547FF2E+ Pin Definition:

#### Pin list:

| PIN No. | PIN NAME    | PIN DESCRIPTION                                             |

|---------|-------------|-------------------------------------------------------------|

| Α       | RF Input    | 950MHz——2150MHz Signal Input Terminal                       |

| В       | RF Output   | 950MHz——2150MHz Signal Output Dispatch                      |

| 1       | B1B         | RF output Voltage supply.                                   |

| 2       | B1A         | LNB Voltage supply.                                         |

| 3,4     | NC          | NC                                                          |

| 5       | B2          | +5V Power Supply                                            |

| 6       | NC          | NC                                                          |

| 7       | AS          | I2C Address Selection: 0(GND or Open) set to D0hex;1(+3.3V) |

|         |             | set to D2hex                                                |

| 7       | I2C Address | GND or Open: 0xd0; +3.3V: 0xd2                              |

| 8       | SDA         | I <sup>2</sup> C DATA Line                                  |

| 9       | SCL         | I <sup>2</sup> C CLOCK Line                                 |

| 10      | DISEQC IN   | 22K Pulse Signal Input For LNB                              |

| 11      | B3          | +3.3V Power Supply                                          |

| 12      | DISEQC OUT  | 22K Pulse Signal Output For LNB                             |

| 13      | VDD         | +2.5V Power Supply                                          |

| 14,, 21 | D0,, D7     | Transport stream output data, D7: Serial Output Data Bus    |

| 22      | BCLK        | Transport stream byte clock output.                         |

| 23      | D/P         | Data Mark Output, 1: Data Output, 0: Parity Output          |

| 24      | STR OUT     | Output "1" for the output of synchronization byte signal.   |

| 25      | ERROR       | Output "1" for the incorrect error occurred.                |

| 26      | RESET       | Reset. Please input "0" for Reset.                          |

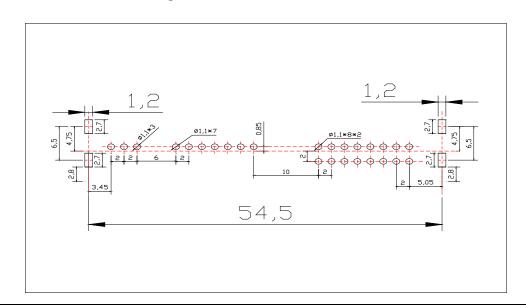

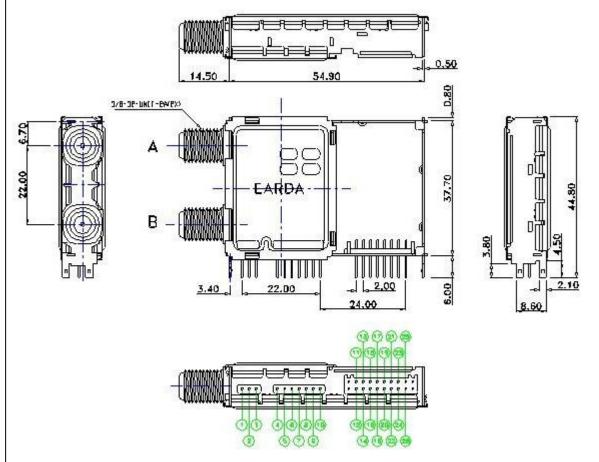

### [12]Dimension for mounting:

#### EDS-1547FF1E+ Dimension

#### **EDS-1547FF1E+ PCB Mounting**